Contact us

Call us at

Available 9 AM - 5 PM CET Business Days

Download

Download Manuals, Datasheets, Software and more:

Feedback

Accurate, Repeatable PCIe Measurements

For nearly two decades, PCI Express® technology has been the widely adopted standard for high-speed serial interface connections. The latest PCIe® specifications address data-intensive markets such as artificial intelligence/machine learning and high-performance computing.

Our PCIe automated test solutions dramatically reduce test complexity by handling setup and calibration.Combined with low noise measurement hardware, these solutions enable fast, accurate, and repeatable signal integrity measurements. As an active voting member of the PCI-SIG® workgroups, we have expertise needed for transmitter, receiver, reference clock, and phase-locked loop (PLL) validation.

PCI Express, PCIE, and PCI-SIG are registered trademarks and/or service marks of PCI-SIG.

Comprehensive Automated Testing Solutions for PCIe

Industry-leading PCIe Base 6.0 Transmitter and Receiver Test Solutions

The recently launched PCIe 6.0 Base specification doubles bandwidth and power efficiency. PCIe 6.0 introduces features such as PAM4 signaling and forward error correction (FEC) to support these high data transfer rates (64.0 GT/s) while maintaining low latency. Tektronix's PCIe 6.0 transmitter (Tx) and receiver (Rx) test solutions enable engineers to address the latest design and validation problems. Intuitive tools provide out-of-the-box support for measurements like signal-to-noise distortion ratio (SNDR) and uncorrelated jitter as well as receiver stressed eye TP3/TP2 calibration and Instrument noise compensation mandated by the latest specifications.

View the PCIe Gen 6.0 Tx Datasheet

View the PCIe Gen 6.0 Rx Datasheet

DPO70000SX ATI Performance Oscilloscopes

PCIe Gen1 to Gen5 Transmitter Test Solutions

Our PCIe transmitter test solutions maintain backward compatibility by offering PCIe transmitter validation and compliance solutions from 2.5 GT/s to 32.0 GT/s ( Gen1 to Gen5). Support spans from early silicon voltage/timing characterization to platform level transmitter and reference clock measurements. Tektronix technology leaders ensure these solutions stay relevant by incorporating all engineering change notices (ECNs) and supporting the PCI-SIG compliance workshops as an approved solution.

View the PCIe Gen 1-5 datasheet

DPO70000SX ATI Performance Oscilloscopes

PCIe Receiver and PLL Test Solutions

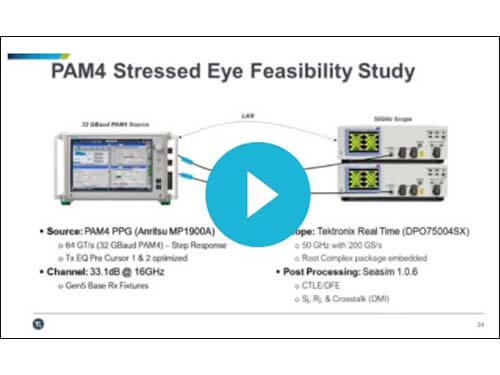

PCIe receiver validation is notoriously difficult due to the sensitivity of calibrating the stressed eye signal across a high loss channel. Tektronix’s PCIe receiver test solutions bring confidence that your design was thoroughly tested at the required bit error rate (BER) target. Our intuitive step-by-step tools provide link training routines for the Anritsu MP1900A BERT to ensure your receiver is tested accurately. Automated testing supports stressed eye calibration, the latest transmitter and receiver link equalization compliance tests, custom BER runs, and jitter tolerance characterization. This framework also powers easy transmitter PLL bandwidth and peaking measurements.

View PCIe receiver test webinar

View the PCIe receiver datasheet

DPO70000SX ATI Performance Oscilloscopes

Fast, Easy PCIe Lane Margining

The TMT4 Margin Tester provides design and validation engineers with a new tool for diagnosing problems at the PCIe physical layer. It evaluates the link health of Gen3 and Gen4 PCIe designs dramatically faster, more easily, and more cost effectively, making it possible to identify problems earlier in the development cycle. Simple to set-up and configure, the TMT4 Margin Tester’s targeted Tx/Rx capability quickly captures issues with PCIe Gen 3 and Gen 4 communications on both ends of the link and enables teams to evaluate the link health of up to x16 Gen 4 links, across all PCIe presets 0-9, in minutes.

Compute Express Link (CXL)

Datacenter architectures must increasingly respond to data movement and access demands while minimizing power, increasing efficiency, and supporting larger and more diverse applications. Building on the strength of the PCIe physical layer, CXL addresses these requirements allowing processors to access the same memory resources efficiently, to talk together, and to run on a single architecture. Physical layer solutions from Tektronix support the fastest CXL data rate (32 GT/s) and diverse form factors expected from this emerging technology.

DPO70000SX ATI Performance Oscilloscopes